橙子的小科普 篇十二:缓存、内存、硬盘?系统能直接装到缓存里吗?

是可以的。而且这个过程没那么复杂,仅从原理来说,冯诺依曼的计算机结构本身,并没有那么复杂,无非就是存储器和计算器的区别。当然,细分起来,它们的原理是有区别的,但是假设基础硬件能够实现,剩下的技术逻辑上并没有那么复杂。

之所以区分了缓存、内存、硬盘,还是因为各个响应时间和速度不同,而需求不同。

缓存→内存→硬盘

缓存→内存→硬盘一级缓存(L1 Cache):大约0.5到1纳秒

二级缓存(L2 Cache):大约2到4纳秒

三级缓存(L3 Cache):大约10到20纳秒

内存(RAM):大约40到100纳秒。这取决于内存的类型(如DDR4、DDR5等)和频率

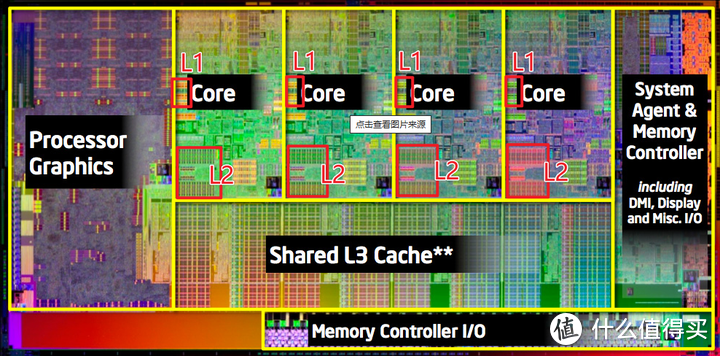

你说为什么大家不都用1ns的缓存呢?当然不是不想,而是这一切都是有代价的。随便找个典型的CPU的切面架构图(因为这个是真实的布局)L1、L2、L3缓存和外置的内存、硬盘最大的区别就是它是和CPU在同一个die上的,也就是说,当硅片上蚀刻出晶体管的时候,它就一并被蚀刻出来了。那么它的空间必然是严重受限的——因为CPU这块die上要蚀刻CPU的内核本身、核显、内存控制器以及其他的芯片比如NPU等等等等。

其次造成它们的性能延迟的不同,则是你看上面的位置,首先L3缓存离的最远,而且是共享的(也不是一定非得共享,看设计,但是现在的主流L3都是共享),L1缓存和L2缓存则是独立服务于一个内核,并且L2缓存在核心边缘,L1缓存则在核心中间,它们的位置当然也不是随便决定的,L1之所以小,就是因为它在中间位置,面积更加难以扩展。近和远就造成了它们的响应速度的不同。

L1、L2、L3缓存的示意图

L1、L2、L3缓存的示意图因为在实际“消耗”晶体管,所以你说L1、L2能不能无限制的增大下去呢?理论上可以,但是大家都知道半导体最要命的就是面积,面积越大,良率越低,成本也就越高,像苹果M系列芯片那么大规模,就基本上只有苹果消化的了那个成本。

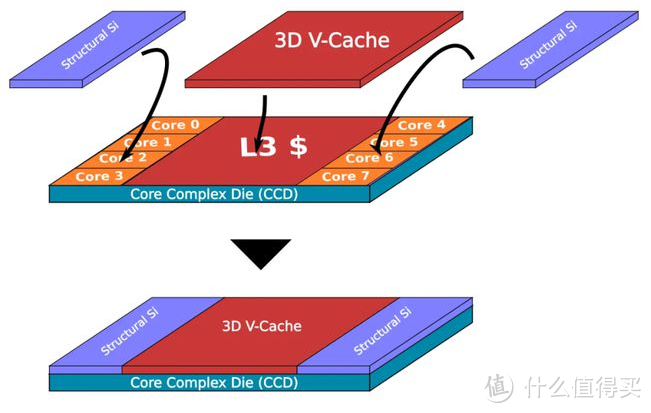

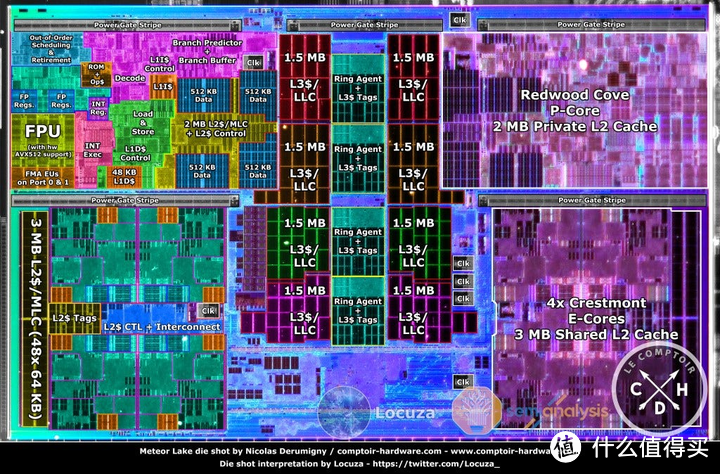

大家知道Intel最新的Meteor Lake更加的“SoC化”了,就是多个芯片被封装在了同一个基板上。但是对于其CPU核心,L1、L2依然是存在于核心内部的。而在Meteor Lake上,最大的遗憾就是没有3D缓存,3D缓存就是如下图,通过3D封装来减少距离减少延迟增加速度。

3D V-Cache

3D V-Cache刚好这里可以给大家看一下,为什么14代Meteor Lake发布的时候,虽然它的实际性能提升还好,主要集中在GPU和AI的NPU上,但是大家对于其新设计还是给了很多肯定,就是因为它的设计其实十分的“新”,几乎改变了以往整个的架构,下面就是它的架构图。

Intel 14代Meteor Lake的透视架构图

Intel 14代Meteor Lake的透视架构图所以总结一下的话,理论上只要L1缓存能够被做的那么大,系统被放到上面并且以最高的性能最低的延迟运行并不是不存在理论可行性的,但是这个理论可行性,又受制于半导体的面积等等问题,导致了成本会高到无法接受。所以大家看到的是KB级的L1、L2缓存,MB级的L3缓存、GB级的内存以及TB级的硬盘,只因为大家设计来的用途不一样,这是平衡了现实制造工艺的一个最优解。

再说个题外话,如果基于一个硅片可以无限蚀刻用担心其面积良率、发热的问题,理论上连独显都可以一并被蚀刻在上面成为“核显”,只不过这个前提是几乎不存在的。

作者声明本文无利益相关,欢迎值友理性交流,和谐讨论~

天降猥人

校验提示文案

iefgiw

校验提示文案

iefgiw

校验提示文案

天降猥人

校验提示文案