硬件技巧 篇159:台积电5nm王之蔑视:171.3MTr/mm²,Intel难以吐槽的晶体管密度

创作立场声明:Tony哥的PC日常

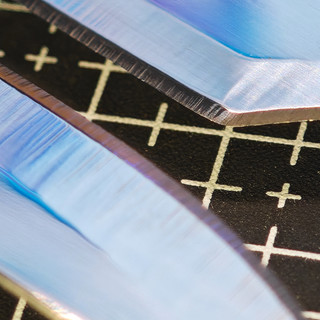

台积电5nm EUV工艺进入试产阶段

相信大家对TSMC(台积电)在晶圆代工领域的绝对制霸地位,早已见惯不怪。在经历了最近5年来摸爬滚打、且战且进的开挂般壮大之后,曾经被Intel抓住小辫子的——晶体管密度,在5nm极紫外光刻工艺的熟用下,以达到其他厂商难以企及的高度。

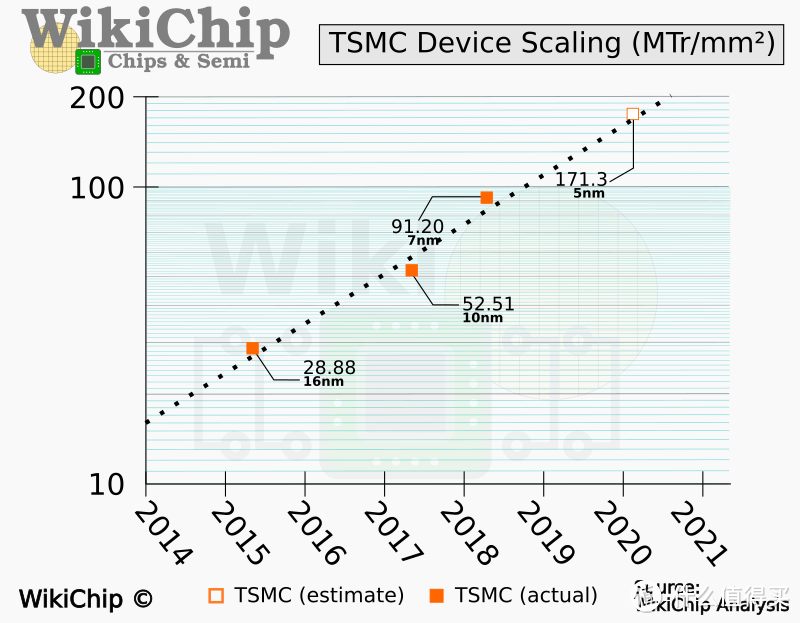

据WikiChips对TSMC新一代5nm EUV光刻工艺的技术指标测算后得出,现阶段(当前5nm试产阶段)台积电5nm EUV工艺的晶体管密度已达到171.3MTr/mm²,也就是每平方毫米容纳了高达1亿7130万个晶体管:

而数年前被Intel多番吐槽的“注水版制造工艺”问题,在上述数字面前基本已无还嘴之力。我们不妨回顾一下近年来TSMC以及其他主要晶圆代工厂,在不同工艺节点对应的晶体管密度表现(从低到高):

台积电16nm:28.2MTr/mm²

三星/格芯14nm:32.5MTr/mm²

台积电12nm:33.8MTr/mm²

格芯12nm:36.7MTr/mm²

Intel 14nm:43.5MTr/mm²

三星10nm:51.8MTr/mm²

台积电10nm:51.8MTr/mm²

三星8nm:60.3MTr/mm²

台积电7nmHPC:66.7MTr/mm²

三星7nm:95.3MTr/mm²

台积电7nmFF+:96.5MTr/mm²

Intel 10nm:100.76MTr/mm²

台积电5nm:171.3MTr/mm²

自2020年3月起,Intel正式从晶体管密度之王的宝座上退位,TSMC迅速即位,并有望在2021年为Intel代工关键产品。而Intel对这个曾经吐槽、蔑视过的公司心悦诚服,结合自身发展趋势,参考AMD一样采用晶圆代工方式生产未来的Intel各类芯片产品。

总结

台积电从16nm的“落后”时代到今天5nm的“会当凌绝顶”,花了5年的时间。在这五年中,台积电量产制程的晶体管密度从28.2MTr/mm²到171.3MTr/mm²翻了6.07倍,似乎又让人看到了一丝摩尔定律生效的迹象。

台积电2014~2021工艺节点&晶体管密度演进参考(注:近似晶体管密度、量产晶体管密度在统计结果上有所不同)

台积电2014~2021工艺节点&晶体管密度演进参考(注:近似晶体管密度、量产晶体管密度在统计结果上有所不同)

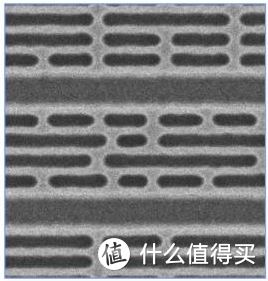

不仅如此,台积电、三星、格芯/IBM等企业正在发力3nm GAA工艺,这一关乎到1nm硅基底材临界点的“终极修罗场”,有望继续让晶体管密度向着更高记录冲刺,谁能最先夺魁?目前来看似乎是台积电最有把握,让我们一起拭目以待吧(๑•̀ㅂ•́)و✧

感谢阅读本文,期待您的点赞+关注,我们下期内容再见ヾ(•ω•`)o~

感谢阅读本文,期待您的点赞+关注,我们下期内容再见ヾ(•ω•`)o~

打倒水军

校验提示文案

打倒水军

校验提示文案